在从事五年专业 PHP 开发后,作者回顾了这门语言的演变。他指出,尽管 PHP 已经发展成为一种功能强大的通用工具,但其内部依然存在一些反直觉的特性,容易导致严重的程序错误。

文中着重提出了两个主要的痛点:

1. **数组(Arrays):** PHP 的“数组”实际上是有序的键值字典。这种灵活性导致了“抽象泄漏”:常规操作(如过滤或删除元素)会破坏索引顺序,迫使开发者必须手动使用 `array_values()` 来重置索引,以避免逻辑错误。

2. **类型属性(Typed Properties):** 作为一门动态语言,PHP 的类型系统深受其历史包袱的掣肘。类型属性存在一种区别于 `NULL` 的“未初始化”状态;访问该状态会导致致命错误,而不是返回默认值。这使得编写防御性代码变得困难,开发者不得不频繁地混合使用 `isset()` 和 `is_null()` 等函数。

尽管存在这些怪癖,作者依然肯定了 PHP 的价值,认为其较低的开发门槛和如 Laravel 这类强大的框架,使其依然是一个实用且可行的选择。他总结道,想要在 PHP 开发中取得成功,必须深入理解其权衡之处,并学会顺应其设计思路去编写代码。

在从事五年专业 PHP 开发后,作者回顾了这门语言的演变。他指出,尽管 PHP 已经发展成为一种功能强大的通用工具,但其内部依然存在一些反直觉的特性,容易导致严重的程序错误。

文中着重提出了两个主要的痛点:

1. **数组(Arrays):** PHP 的“数组”实际上是有序的键值字典。这种灵活性导致了“抽象泄漏”:常规操作(如过滤或删除元素)会破坏索引顺序,迫使开发者必须手动使用 `array_values()` 来重置索引,以避免逻辑错误。

2. **类型属性(Typed Properties):** 作为一门动态语言,PHP 的类型系统深受其历史包袱的掣肘。类型属性存在一种区别于 `NULL` 的“未初始化”状态;访问该状态会导致致命错误,而不是返回默认值。这使得编写防御性代码变得困难,开发者不得不频繁地混合使用 `isset()` 和 `is_null()` 等函数。

尽管存在这些怪癖,作者依然肯定了 PHP 的价值,认为其较低的开发门槛和如 Laravel 这类强大的框架,使其依然是一个实用且可行的选择。他总结道,想要在 PHP 开发中取得成功,必须深入理解其权衡之处,并学会顺应其设计思路去编写代码。

每日HackerNews RSS

与其将大语言模型生成的代码视为需要人工审查的对象,作者认为我们应将其视为一种新型的“机器代码”。由于大语言模型的输出具有非确定性和高产出量的特点,传统的代码审查正变得不再适用。 然而,这种转变需要审慎的组织策略,而非个人的选择。为了获得真正的生产力提升,企业必须摒弃传统的开发流程(如基于工单的任务分配和人工把关机制),转而采用自主的、以智能体为驱动的流程。由于重构成本显著降低,工程严谨性的重心必须从代码本身转移到对工作内容的定义上。 作者提出,“知识单元”应转变为标准化的、版本可控的规范以及强大的自动化测试套件。在这种模式下,责任在于维护清晰的规范并验证生成代码是否符合要求,而不是手动审计每一行输出。通过重构组织流程以应对“无限”的需求供给,并优先进行规范驱动的开发,团队便能在不牺牲项目完整性的前提下,有效利用大语言模型。

在1880年出版的《挣钱的艺术》(*The Art of Money Getting*)一书中,传奇演艺家P.T.巴纳姆将其一生关于财富与成功的经验提炼为20条实用准则。巴纳姆曾历经巅峰声望与破产困境,他为实现职业与个人稳定提供了永恒的建议。

其核心哲学基于四大支柱:

1. **从事适合你的职业:** 当你从事与自身天赋相符的工作时,成功会更容易。

2. **避免债务:** 债务会损害你的自由与自尊;务必量入为出。

3. **全力以赴:** 三心二意只会导致平庸。若想出类拔萃,必须在每一项任务中竭尽全力。

4. **坚守诚信:** 信誉是你最宝贵的资产;不诚实的做法或许能带来短期收益,却会摧毁长远的潜力。

巴纳姆曾有名言警示:“金钱是极好的仆人,却是可怕的主人。”通过掌握这些原则——专注于你的“专长”、消除债务、高效工作并诚实守信,你便能掌控自己的财务生活。最终,巴纳姆提倡一种有目标的生活,让一个人的工作成为其品格与真实潜力的体现。

在1880年出版的《挣钱的艺术》(*The Art of Money Getting*)一书中,传奇演艺家P.T.巴纳姆将其一生关于财富与成功的经验提炼为20条实用准则。巴纳姆曾历经巅峰声望与破产困境,他为实现职业与个人稳定提供了永恒的建议。

其核心哲学基于四大支柱:

1. **从事适合你的职业:** 当你从事与自身天赋相符的工作时,成功会更容易。

2. **避免债务:** 债务会损害你的自由与自尊;务必量入为出。

3. **全力以赴:** 三心二意只会导致平庸。若想出类拔萃,必须在每一项任务中竭尽全力。

4. **坚守诚信:** 信誉是你最宝贵的资产;不诚实的做法或许能带来短期收益,却会摧毁长远的潜力。

巴纳姆曾有名言警示:“金钱是极好的仆人,却是可怕的主人。”通过掌握这些原则——专注于你的“专长”、消除债务、高效工作并诚实守信,你便能掌控自己的财务生活。最终,巴纳姆提倡一种有目标的生活,让一个人的工作成为其品格与真实潜力的体现。

本周新闻重点关注了隐私、安全及执法技术领域的重大进展。主要更新包括《移除法案》(Take It Down Act)的颁布,该法案旨在帮助受害者移除未经同意的私密照片;此外,针对数据经纪商操纵性退订流程的打击力度也在加大。同时,美国联邦贸易委员会(FTC)就无效的“主动监听”广告技术与多家营销公司达成和解。 在监控领域,争议不断:尽管一些立法者试图限制该技术的使用,联邦调查局(FBI)仍寻求数百万美元资金,以获取全国范围内的实时车牌识别(ALPR)数据。在网络安全方面,GitHub 遭遇了 TeamPCP 组织的攻击;谷歌则意外泄露了一个尚未修复的重大 Chromium 漏洞,该漏洞允许攻击者劫持浏览器进行持续监控或开展僵尸网络活动。 其他值得关注的新闻还包括:针对一名前警官为美国移民及海关执法局(ICE)提供枪支训练的调查,一名警察与麦迪逊广场花园之间的法律纠纷,以及欧洲国家寻求“无美国参与”的技术替代方案。此外,特朗普政府与硅谷之间的纠葛持续影响着全球科技政策。

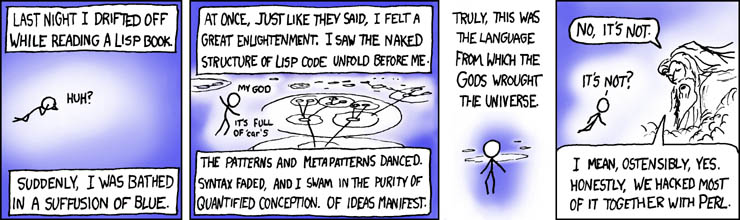

本文概述了在 Vim 中配置 Lisp 开发环境的方法,主要介绍了两款主流插件:**Slimv** 和 **Vlime**。这两款插件均采用了与 Emacs 的 SLIME 类似的客户端-服务器架构,通过连接至 Swank 服务器,为 Vim 提供交互式 REPL、基于 Paredit 的结构化编辑、调试以及宏展开等功能。

**核心对比点:**

* **安装:** Slimv 遵循标准的 Vim 目录结构,安装过程比 Vlime 更简便(Vlime 需要手动配置运行时路径)。

* **要求:** Slimv 要求 Vim 支持 Python,而 Vlime 则无此要求。

* **功能:** Slimv 的 REPL 交互性更强,并支持 Common Lisp、Scheme 和 Clojure。Vlime 仅限于 Common Lisp,且采用独立窗口显示信息,对部分用户而言可能不够便捷。

* **Paredit 集成:** Slimv 内置了 Paredit,其集成度比 Vlime 更顺畅。

作者推荐使用 **Slimv**,因为它更为成熟,支持的语言更广泛,且用户体验更直观。不过,也建议读者亲自尝试两者,以确定哪一个更契合自己的工作流。文中还提供了针对不同 Lisp 实现(如 SBCL、CLISP、ECL)的详细设置指南及故障排除建议。

本文概述了在 Vim 中配置 Lisp 开发环境的方法,主要介绍了两款主流插件:**Slimv** 和 **Vlime**。这两款插件均采用了与 Emacs 的 SLIME 类似的客户端-服务器架构,通过连接至 Swank 服务器,为 Vim 提供交互式 REPL、基于 Paredit 的结构化编辑、调试以及宏展开等功能。

**核心对比点:**

* **安装:** Slimv 遵循标准的 Vim 目录结构,安装过程比 Vlime 更简便(Vlime 需要手动配置运行时路径)。

* **要求:** Slimv 要求 Vim 支持 Python,而 Vlime 则无此要求。

* **功能:** Slimv 的 REPL 交互性更强,并支持 Common Lisp、Scheme 和 Clojure。Vlime 仅限于 Common Lisp,且采用独立窗口显示信息,对部分用户而言可能不够便捷。

* **Paredit 集成:** Slimv 内置了 Paredit,其集成度比 Vlime 更顺畅。

作者推荐使用 **Slimv**,因为它更为成熟,支持的语言更广泛,且用户体验更直观。不过,也建议读者亲自尝试两者,以确定哪一个更契合自己的工作流。文中还提供了针对不同 Lisp 实现(如 SBCL、CLISP、ECL)的详细设置指南及故障排除建议。

**z386** 是一款基于 FPGA 的 CPU,旨在通过恢复的微代码而非传统的 RTL 仿真器来复刻英特尔 80386 架构。z386 在 z8086 项目成功的基础上构建,既是一项教育性的重构工程,也是一款功能齐全的处理器,能够运行真实的保护模式 DOS 软件,包括 DOS/4GW 扩展程序以及《毁灭战士》(Doom)等游戏。

在架构上,z386 模仿了 80386 的“协作单元”结构——包含预取单元、解码器、微代码定序器以及分段/分页单元——而非现代的 RISC 流水线。它融合了针对 FPGA 优化的捷径,例如 16KB VIPT(虚拟索引,物理标记)L1 缓存和基于 DSP 的乘法运算,从而实现了高性能(约 70–85MHz)。

该项目成功架起了硬件考古与现代应用之间的桥梁,提供了高保真的 386 使用体验。尽管其 CPI(每指令周期数)高于 ao486 等现代实现,但它在历史准确性和可用系统性能之间取得了独特的平衡。通过针对 BIOS、DOS 扩展程序和单步模糊测试的严格测试,该项目持续演进,成为重构定义现代 x86 时代架构过程中的一个重要里程碑。

**z386** 是一款基于 FPGA 的 CPU,旨在通过恢复的微代码而非传统的 RTL 仿真器来复刻英特尔 80386 架构。z386 在 z8086 项目成功的基础上构建,既是一项教育性的重构工程,也是一款功能齐全的处理器,能够运行真实的保护模式 DOS 软件,包括 DOS/4GW 扩展程序以及《毁灭战士》(Doom)等游戏。

在架构上,z386 模仿了 80386 的“协作单元”结构——包含预取单元、解码器、微代码定序器以及分段/分页单元——而非现代的 RISC 流水线。它融合了针对 FPGA 优化的捷径,例如 16KB VIPT(虚拟索引,物理标记)L1 缓存和基于 DSP 的乘法运算,从而实现了高性能(约 70–85MHz)。

该项目成功架起了硬件考古与现代应用之间的桥梁,提供了高保真的 386 使用体验。尽管其 CPI(每指令周期数)高于 ao486 等现代实现,但它在历史准确性和可用系统性能之间取得了独特的平衡。通过针对 BIOS、DOS 扩展程序和单步模糊测试的严格测试,该项目持续演进,成为重构定义现代 x86 时代架构过程中的一个重要里程碑。

本摘要探讨了将 Rendezvous Hashing (HRW) 作为 Elixir 分布式键映射的一种无状态函数式替代方案,以取代 `ExHashRing`。 虽然 `ExHashRing` 是业界公认的标准,但它需要管理有状态的受监督进程。相比之下,HRW 提供了一种更简单的纯函数式方法,通过计算键在各节点上的权重来确定归属。 其中的权衡在于性能复杂度。基础的 HRW 实现复杂度为 $O(n)$,即与节点数量呈线性关系,随着集群规模扩大,速度可能会变慢。然而,作者引入了一种“骨架(skeleton)”优化,实现了 $O(\log n)$ 的性能,使其速度达到与 `ExHashRing` 相近的水平,且无需维护有状态进程。 基准测试表明,HRW 提供了出色的分布效果,在节点数量较多时,其表现往往优于可能需要增加虚拟节点配置才能维持性能的 `ExHashRing`。作者已在 Hex 上发布了 `hrw` 库,支持基础、骨架、加权和有界策略,为分布式 Elixir 应用提供了一种灵活且轻量级的替代方案。

作者调查了“Zork”这一名称的词源,并特别针对其源于麻省理工学院黑客术语中“未完成程序”这一常见说法提出了质疑。

在分析了维基百科的编辑历史及相互冲突的历史资料后,作者发现了矛盾之处:一方面,有来源(蒂姆·安德森)声称这是指代未完成工作的术语;但另一方面,包括游戏创作者在内的多位人士在当代访谈中,均将“zork”简单地定义为类似于“foobar”或“frob”的无意义词汇。此外,对理查德·斯托曼(Richard M. Stallman)和理查德·加布里埃尔(Richard P. Gabriel)等20世纪70年代麻省理工学院校友的咨询结果显示,并无证据证实“zork”曾被用作指代未完成软件的术语。

作者认为,该定义很可能缺乏广泛的历史支持,并可能是由于维基百科未经证实的编辑而得以流传。作者对此持怀疑态度,并指出如果它真的是标准术语,理应像“hack”或“foobar”一样保留在计算词汇中。作者邀请任何曾亲身经历过将“zork”用作“未完成程序”同义词的人士提供线索,希望能借此还原历史真相。

作者调查了“Zork”这一名称的词源,并特别针对其源于麻省理工学院黑客术语中“未完成程序”这一常见说法提出了质疑。

在分析了维基百科的编辑历史及相互冲突的历史资料后,作者发现了矛盾之处:一方面,有来源(蒂姆·安德森)声称这是指代未完成工作的术语;但另一方面,包括游戏创作者在内的多位人士在当代访谈中,均将“zork”简单地定义为类似于“foobar”或“frob”的无意义词汇。此外,对理查德·斯托曼(Richard M. Stallman)和理查德·加布里埃尔(Richard P. Gabriel)等20世纪70年代麻省理工学院校友的咨询结果显示,并无证据证实“zork”曾被用作指代未完成软件的术语。

作者认为,该定义很可能缺乏广泛的历史支持,并可能是由于维基百科未经证实的编辑而得以流传。作者对此持怀疑态度,并指出如果它真的是标准术语,理应像“hack”或“foobar”一样保留在计算词汇中。作者邀请任何曾亲身经历过将“zork”用作“未完成程序”同义词的人士提供线索,希望能借此还原历史真相。